# A Fast Track Trigger (FTT) for H1 at HERA (DESY)

**David Meer**

### Content

- Overview H1 (Trigger)

- Concept of the FTT

- Physical motivation and benefit

- Hardware

- L2: Linking

- Summary

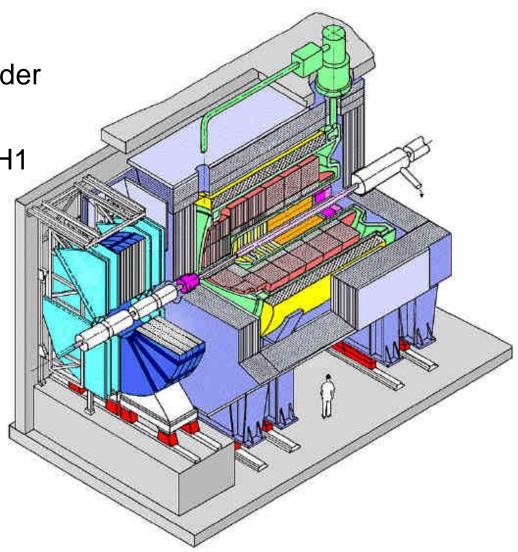

### **Overview: Detector**

- HERA: e<sup>±</sup> (30 GeV) p<sup>+</sup> (820 GEV) collider √s = 320 GeV

- Main detector components of H1

- tracking chambers

- Calorimeters (el., hadronic)

- muon chambers

- Shutdown in september 2000 for luminosity upgrade

- Opportunity to upgrade detector (~18 projects)

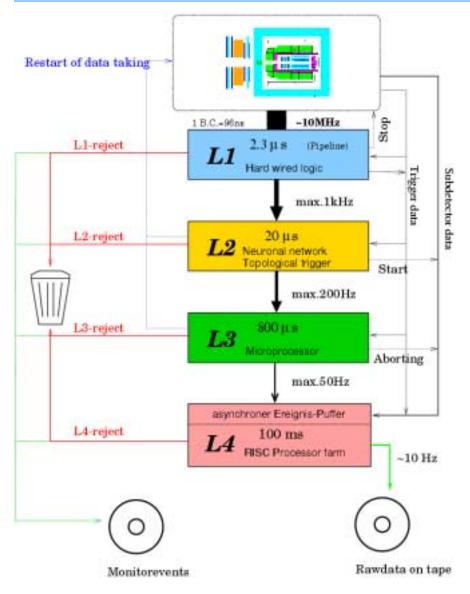

# **Overview: Trigger**

- L3 was not enabled

- Exclusive final state reconstuction only at L4

- Iuminosity increase about factor 5

- Downscaling with prescale factors

| Q²  | Prescale |      | officionov |

|-----|----------|------|------------|

|     | today    | 2001 | efficiency |

| 5   | 5        | 25   | 4 %        |

| 50  | 2        | 10   | 10 %       |

| 150 | 1        | 1    | 100 %      |

```

=> A fast track trigger

```

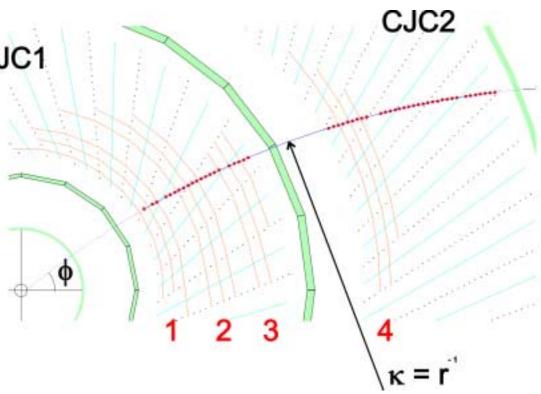

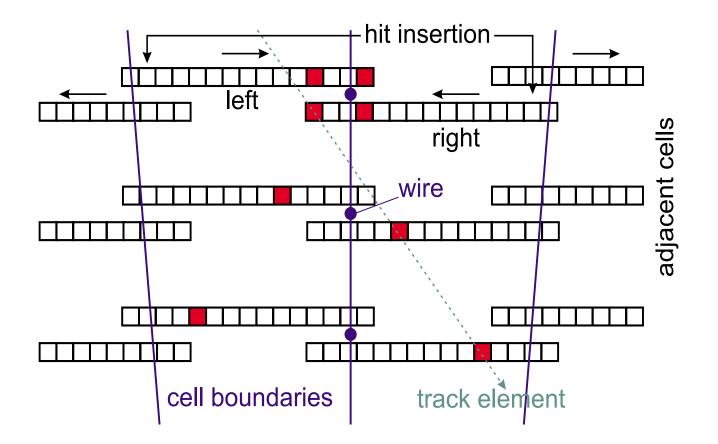

# **Concept of the FTT**

- FTT in parallel to existing CJC1 trigger

- FTT is based on a subset of CJC wires

- 4 layers groups with 3 wires each

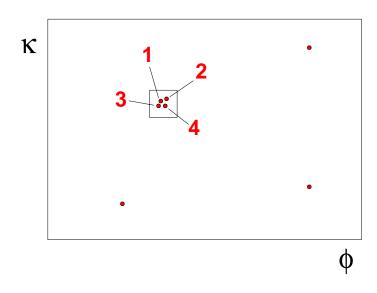

- 2d linking in  $\kappa$ - $\phi$  plane

- refit track parameters and take trigger decision

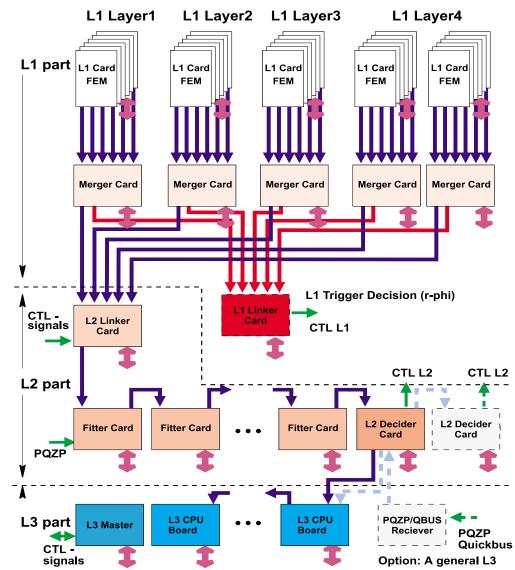

# **Trigger levels on FTT**

|                          | L1                                                   | L2                           | L3                       |

|--------------------------|------------------------------------------------------|------------------------------|--------------------------|

| Latency                  | 2.3 μs                                               | 25 µs                        | ≈ 100 µs                 |

| Tasks                    | Q–t analysis,<br>track segment<br>finding            | linking of track<br>segments | event<br>reconstruction  |

| Data used<br>for trigger | coarsely linked<br>track segment                     | measured tracks              | combination of<br>tracks |

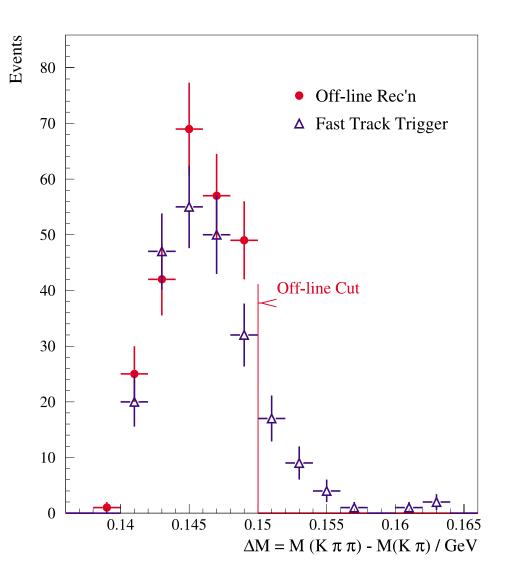

| Trigger<br>decision on   | p <sub>⊤</sub> thresholds<br>multiplicity<br>charges | full track<br>information    | invariant<br>masses, ∆m  |

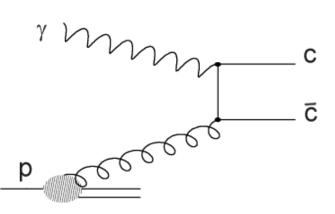

# **Physical Motivation**

Example: Measurement of gluon content of a proton in open charm production

Identification through decay channel

D<sup>\*</sup> → D<sup>0</sup> π<sub>slow</sub> → K π π<sub>slow</sub>

• Cut on  $\Delta m = m(K \pi \pi_{slow}) - m(K \pi)$

# **Physical Benefit**

| Process                        | efficiency | efficiency   |  |

|--------------------------------|------------|--------------|--|

| F100835                        | FTT [%]    | prescale [%] |  |

| D <sup>*</sup> decay (DIS)     | 70         | 1            |  |

| D <sup>*</sup> decay (γp)      | 60         | 1            |  |

| $\rho \rightarrow \pi^+ \pi^-$ | 80         | 2            |  |

| J/Ψ → μμ (ee)                  | 60 (12)    | 3 (1)        |  |

| $Y \rightarrow \mu\mu$ (ee)    | 60 (12)    | 3 (1)        |  |

| W → μυ                         | 70         | 3 (1)        |  |

• Resolution of FTT from D<sup>\*</sup> events (=> Binning of the  $\kappa$ - $\phi$  plane):

$$\sigma\left(\frac{1}{p_{\tau}}\right) = 0.04 \frac{1}{\text{GeV}} \qquad \sigma(\phi) = 6 \text{ mrad}$$

z information calculated from charge divison

$\sigma(z) \approx 4 \, \mathrm{cm} \implies \sigma(\theta) = 50 \, \mathrm{mrad}$

### Hardware: Overview

#### • L1:

- Flash ADC (80 MHz)

- hits are filled in shift registers

- compare hit pattern to valid masks (several 1000)

- total 30 FEM

#### • L2:

- collect all track segment

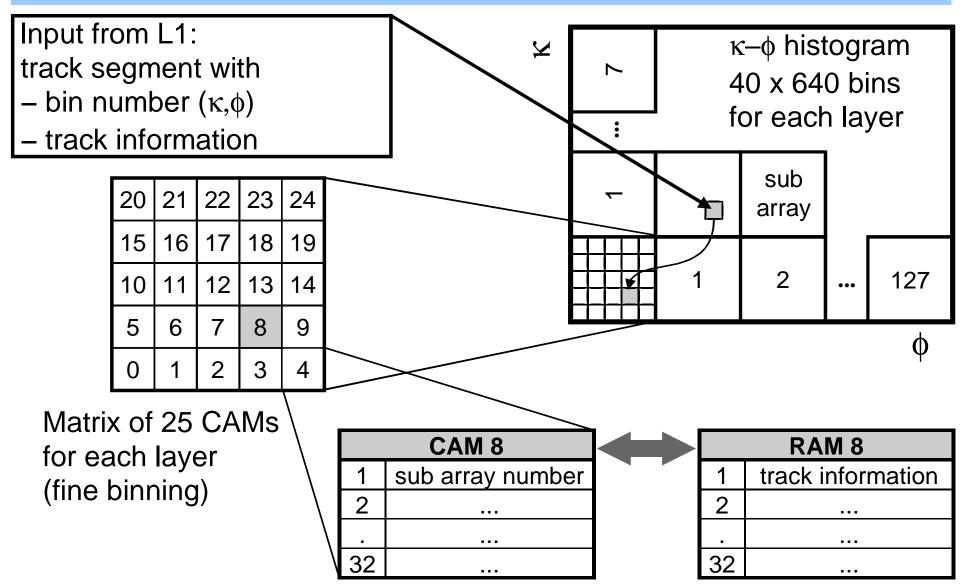

- linking in  $\kappa$ – $\phi$  histogram

- non iterativ circle fit on DSP

- 1 multipurpose card

- L3:

- commercial board with 450 MHz PowerPC750

- 4–16 PPC

### **Track segment finding**

### Hardware: FPGA

- Modern programmable chips: FPGA (Field Programmable Gate Array)

- High density of gates (> 1 million)

- speed: 100 MHz or more, number of I/O pins > 400

- Programmed logic can be modified any time (via VME)

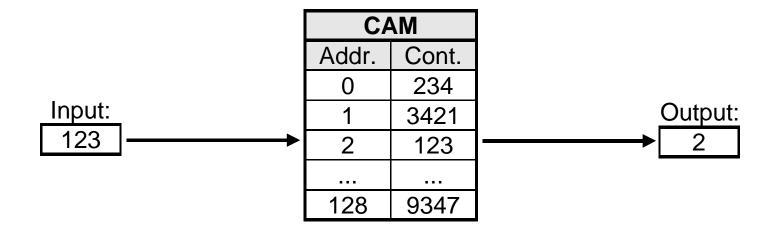

- Key technique for FTT: CAM (Content addressable memory)

### Hardware: Development

• Institutes involved in the project:

| L1 | Rutherford Appleton Lab      |  |

|----|------------------------------|--|

|    | Uni of Manchester            |  |

|    | Uni of Birmingham            |  |

| L2 | Supercomputing Systems (SCS) |  |

|    | ETH Zürich                   |  |

|    | Uni Dortmund                 |  |

| L3 | Uni Dortmund                 |  |

- Development status:

- feasibility has been shown

- hardware is in design stage

# L2 linking: κ–φ histogram

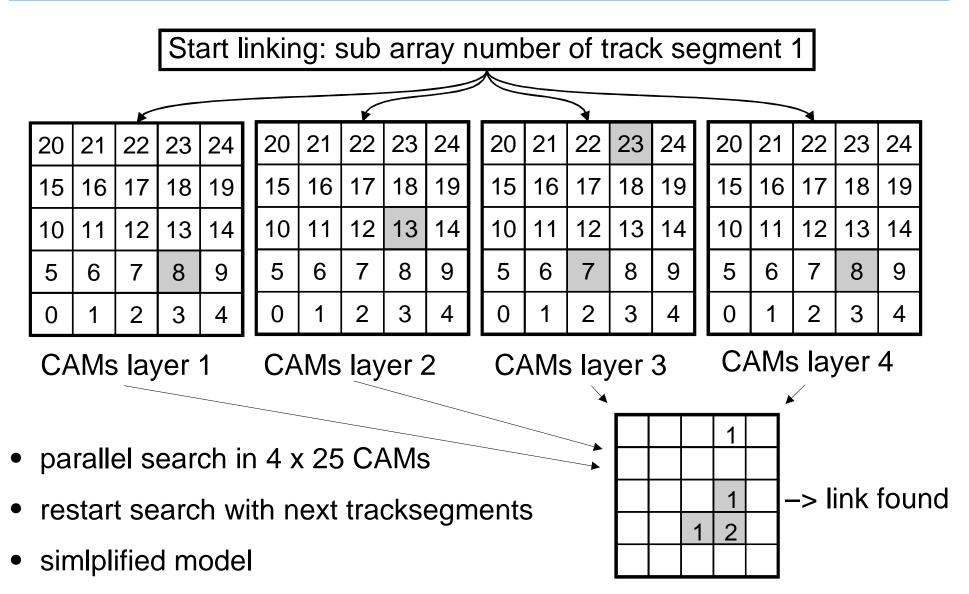

# L2 linking: link track segments

### Summary

- Exclusive track based triggering is necessary after HERA luminosity upgrade

- FTT is a very flexibel system (hardware & trigger)

- Good integration of FTT in the existing trigger

- FTT provides L1–, L2– and L3–keep signal

- Realisation possible due to chip development of past years

- FTT is fast:

- process 40'000 events per second

- recunstruct 2 million tracks per second